University of Balearic Islands Department of Physics Electronic Systems Group

PhD. Thesis

# An advanced Framework for efficient IC optimization based on analytical models engine

Author: Salvador Barceló Adrover Director: Dr. Jaume Segura

Esta tesis doctoral ha sido realizada por el Sr. Salvador Barceló Adrover bajo la dirección del Dr. Jaume Segura Fuster, del Departamento de Física de la Universidad de las Islas Baleares (UIB).

Palma de Mallorca, 6 de noviembre de 2013

Dr. Jaume Segura Fuster

El director de tesis

Salvador Barceló Adrover El doctorando

La realización de esta tesis doctoral ha estado financiada por el proyecto TEC20011-25017 del Ministerio de Ciencia e Innovación y ha recibido una ayuda para apoyar a grupos de investigación competitivos de la Consejería de Educación, Cultura y Universidades del Gobierno Balear (2011-2013), patrocinada por la Comunidad Autónoma de las Illes Balears y cofinanciada con fondos FEDER. También ha contado con una beca de formación de personal investigador (FPI) del Ministerio de Ciencia e Innovación (BES-2006-11943).

## Resumen de la tesis

El escalado de la tecnología CMOS ofrece grandes ventajas tales como el aumento de la densidad de integración o la frecuencia de operación a la par que proporciona una reducción del consumo de energía y el coste por transistor. Esta carrera por la integración genera nuevos desafíos relacionados con efectos adversos, algunos son de nueva aparición mientras que otros se agravan respecto a nodos anteriores . Uno de tales efectos adversos de importancia creciente es el impacto de los llamados Single Event Transient o SET . Dado que el escalado de la tecnología reduce la capacidad parásita de los nodos internos, la tensión de alimentación y el retardo de puerta, la importancia relativa del efecto de las partículas ionizantes aumenta debido a que la misma cantidad de carga es capaz de inducir un transitorio de tensión con mayor probabilidad de propagarse dentro del circuito.

Además de las técnicas basadas en redundancia, muchas soluciones de mitigación se basan en el aumento de la robustez intrínseca del circuito frente a eventos transitorios. Aunque estas estrategias no pueden evitar el problema completamente, reducen su impacto hasta límites aceptables dependiendo del ámbito de aplicación del circuito.

En base a estos desafíos, la presente tesis desarrolla y analiza un conjunto de herramientas orientadas a la evaluación de la sensibilidad a la propagación de eventos SET en circuitos microelectrónicos. Las herramientas de procesamiento son capaces de manejar circuitos con una alta complejidad de forma eficiente.

Después de desarrollar un sistema compacto de lógica específica que mejora el rendimiento de los algoritmos construidos para propagar las transiciones dentro del circuito y manejar de forma eficiente la propagación de SETs, se presentan diversas técnicas de simplificación, partición y encapsulación de bloques en circuitos.

Se ha desarrollado un algoritmo eficiente de búsqueda de caminos sensibilizables cuya eficacia se ha demostrado sobre circuitos tipo benchmark de tamaño considerable. Se ha demostrado también que el tiempo de retardo de un camino dado depende de los vectores de sensibilización aplicados a las puertas complejas que forman parte del mismo. En algunos casos, la variación de retardo debida a los diferentes vectores de sensibilización es comparable a las variaciones de retardo

atribuibles a las variaciones paramétricas del proceso.

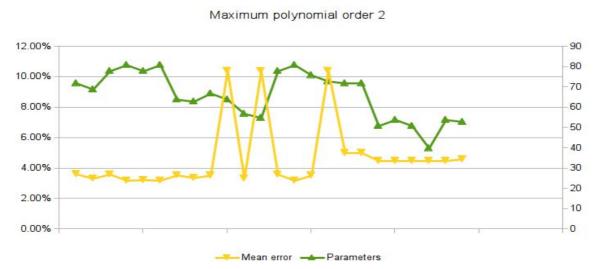

El motor del algoritmo de análisis de SET a nivel de circuito lo constituye un modelo analítico de propagación de SET a nivel de puerta lógica (desarrollado en el marco de otra tesis doctoral en desarrollo) implementado mediante un ajuste polinómico. Los coeficientes del modelo son extraídos para cada tecnología a partir del tratamiento automatizado de la biblioteca de puertas lógicas correspondiente. El proceso de extracción determina el conjunto de parámetros óptimo para cada puerta de la biblioteca, constituyendo un proceso clave para una estimación precisa de la propagación de SETs a nivel de circuito.

Después de verificar la descripción de la propagación de SET a través de un trabajo exhaustivo de simulación a nivel eléctrico, utilizando circuitos de tipo benchmark sintetizados en tecnologías CMOS comerciales, se han propuesto varias métricas de propagación de SETs considerando el impacto de los enmascaramientos lógico, eléctrico y combinado lógico-eléctrico. Estas métricas proporcionan una vía de análisis para cuantificar tanto las regiones que son más susceptibles a propagar eventos SET hacia las salidas como el conjunto de salidas más susceptibles de producir eventos SET.

La aplicación de la herramienta a circuitos tipo benchmark grandes han demostrado la capacidad del conjunto de herramientas en el ámbito de la estimación de la propagación de SETs. En base a los indicadores desarrollados, la herramienta es capaz de identificar la lista de nodos internos que son más susceptibles a propagar un SET, considerando tanto los efectos de enmascaramiento eléctrico como lógico. Los resultados pueden ser ponderados por la probabilidad lógica de que un cierto camino se encuentre sensibilizado a partir de los vectores de entrada del circuito . Del mismo modo, la herramienta también proporciona información acerca de los nodos de salida del circuito con una mayor probabilidad de producir un SET en ambientes de radiación específicos.

Un análisis adicional permite determinar exhaustivamente el efecto de ensanchamiento/filtrado del pulso inyectado de forma exhaustiva en todos los nodos del circuito.

La aplicación exhaustiva de la herramienta al análisis de los circuitos tipo benchmark grandes demuestra la viabilidad de las mismas para el tratamiento de grandes circuitos obteniendo la información de interés.

En numerosos casos, el conjunto de algoritmos desarrollados han proporcionado mejores resultados que las herramientas comerciales consideradas estándar en ámbitos industriales.

### Abstract

CMOS IC technology scaling provides many advantages like integration density increase, higher operating frequency while providing reduced power consumption and cost per transistor. Such integration race generates new challenges related to adverse side effects some of them being new, while others are exacerbated from previous technology nodes. One of such adverse effect that grows in importance is the impact of Single Event Transients (SETs). As technology scaling reduces the parasitic capacitance, supply voltage and the gate delay, the relative importance of ionizing particles increases because the same amount of charge is capable of inducing a voltage transient that may propagate within the circuit.

Apart of redundancy-based techniques, many mitigation solutions are based on increasing the circuit intrinsic robustness to soft-error effects. Although these strategies cannot avoid the problem completely, they reduce the soft-error impact to an acceptable limit that depends on the circuit application.

Based on these challenges, this thesis develops and evaluates a complete framework for SET propagation sensitivity. The framework comprises a number of processing tools capable of handling circuits with high complexity in an efficient way.

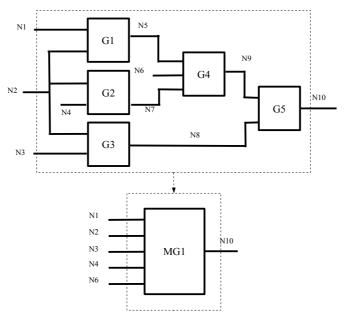

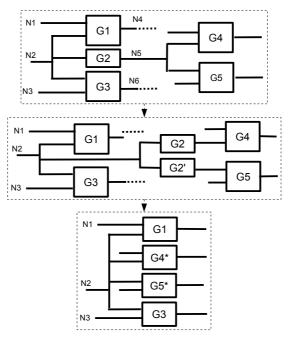

After developing a compact specific logic system to enhance the performance of the algorithms constructed to propagate transitions within the circuit and handle efficiently SET propagation, various simplification, partitioning and encapsulation techniques have been detailed and analyzed to enhance the overall framework operation.

A quite efficient true path finding algorithm has been constructed and its efficacy demonstrated on large benchmark circuits. It has been also shown that the delay of a given path depends on the sensitization vectors applied to the complex library gates within the path. In some cases, the delay variation due to different sensitization vectors is comparable to the path delay caused by process parameters variations. Such an improvement over the path delay computation, links such delay estimation to the specific sensitization vector and to the verification of the path being a true path, representing a significant improvement over commercial tools.

The framework developed engine is an SET analytical propagation model (developed within

another Ph.D. thesis under development) incorporated as a polynomial implementation. Polynomial coefficients are extracted for each technology by automatically processing the associated gate library. An optimal parameter set is obtained for each library gate, being a key process for accurate SET propagation estimation.

After verifying the SET propagation description through extensive electrical simulations over benchmark circuits synthesized on commercial CMOS technologies, various SET propagation metrics have been proposed considering the impact of logic masking, electric masking and combined logic-electric masking. Such metrics provide a valuable vehicle to grade either in-circuit regions being more susceptible of propagating SET events toward the circuit outputs or circuit outputs more susceptible to produce SET events.

The tool application to large benchmark circuits has shown the framework capabilities in the SET propagation estimation domain. Based on the developed metrics, the tool is capable of identifying the list of circuit internal nodes most suitable to propagate an SET accounting for both the electrical and logical masking effects. Results can be weighted by the logic probability of a node being activated from the circuit input vectors. Similarly, the tool also provides information about the circuit output nodes with a higher probability of producing an SET under specific radiation environments. An additional tool analysis determines exhaustively the effect of pulse broadening/filtering once a specific SET event is induced at each circuit node.

Exhaustive application to large benchmark circuits demonstrates the framework feasibility to treat huge circuits providing the parameters of interest. In many instances, the developed framework has been shown to output better results than industry-standard commercial tools.

# Index

| Chapter 1: Introduction                                     | 1  |

|-------------------------------------------------------------|----|

| 1.1.Motivation and objectives                               | 2  |

| 1.2.Document organization.                                  | 4  |

| Chapter 2: Timing analysis and SET propagation              | 5  |

|                                                             |    |

| 2.1.Timing analysis                                         |    |

| 2.2.Delay modeling                                          |    |

| 2.2.1.Empirical modeling                                    |    |

| 2.2.1.1. Lookup Table (LOT)                                 |    |

| 2.2.2.Extraction process.                                   |    |

| 2.2.3.Multivariable polynomial model.                       |    |

| 2.2.4.Computational advantages                              |    |

| 2.3.Effective capacitance                                   |    |

| 2.3.1.Capacitance components.                               |    |

| 2.3.1.1. Transistor-level components                        |    |

| 2.4.SET Propagation                                         |    |

|                                                             |    |

| Chapter 3: Framework core elements                          | 29 |

| 3.1.Definitions                                             | 29 |

| 3.2.Logic System                                            | 32 |

| 3.2.1.Theoretical concepts                                  |    |

| 3.2.2.State of the art.                                     | 33 |

| 3.2.3.Developed Logic System                                | 34 |

| 3.2.4.Dual logic system                                     | 38 |

| 3.3.Basic operations                                        | 41 |

| 3.3.1.Sensitization.                                        | 41 |

| 3.3.2.Implication.                                          | 46 |

| 3.3.3.Justification.                                        | 48 |

| 3.4.Sensitization Algorithms                                | 51 |

| 3.4.1.Stepwise algorithm                                    |    |

| 3.4.1.1. Branch point.                                      |    |

| 3.4.1.2. Main routine                                       |    |

| 3.4.1.3. Implication                                        |    |

| 3.4.1.4. Justification                                      |    |

| 3.4.2.Full path algorithm.                                  |    |

| 3.4.3.Path graph creation.                                  | 67 |

| Chapter 4: Preprocessing techniques and Framework structure | 69 |

| 4.1.Simplification techniques.                              | 70 |

| 4.2.Partitioning techniques                                 | 70 |

| 4.2.1.Auxiliary routines.                                   | 70 |

| 4.2.1.1. Touch related nodes algorithm                                  | 70  |

|-------------------------------------------------------------------------|-----|

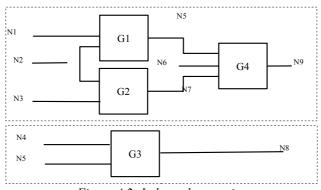

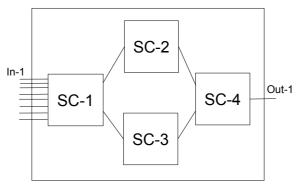

| 4.2.2.Separate independent sections                                     | 71  |

| 4.2.3.Partitioning by Output                                            | 73  |

| 4.2.4.Partitioning by Input                                             | 74  |

| 4.2.5.Partitioning by Input-Output                                      |     |

| 4.3.Encapsulation techniques.                                           |     |

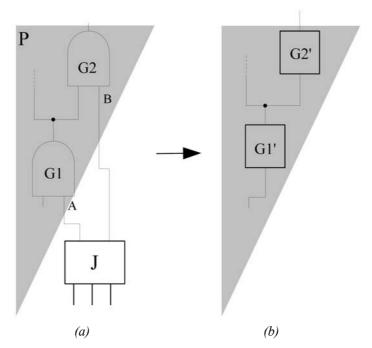

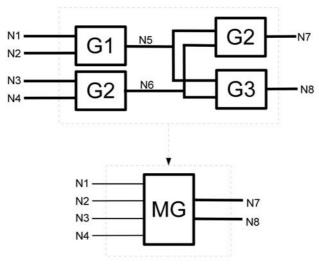

| 4.3.1.Principle of the technique                                        |     |

| 4.3.2.Specific techniques                                               |     |

| 4.3.2.1. Gates with special input configuration                         |     |

| 4.3.2.2. Non-Stem nodes.                                                | 85  |

| 4.3.2.3. Reconvergent fan-out                                           |     |

| 4.3.2.4. Single input gates                                             |     |

| 4.3.2.5. Gates sharing all inputs nodes                                 |     |

| 4.3.2.6. Gates partially sharing input nodes.                           |     |

| 4.4.Application                                                         |     |

| 4.4.1.Identification of repeated structures                             |     |

| 4.4.2.Path enumeration.                                                 |     |

| 4.5.Results                                                             | 97  |

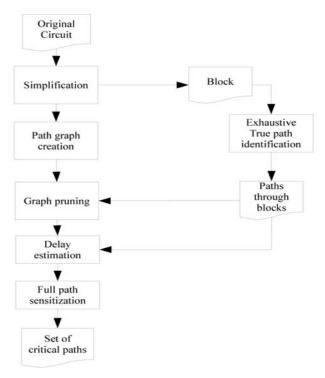

| 4.6.Framework                                                           | 102 |

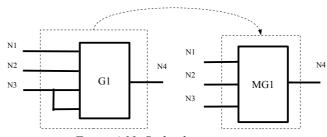

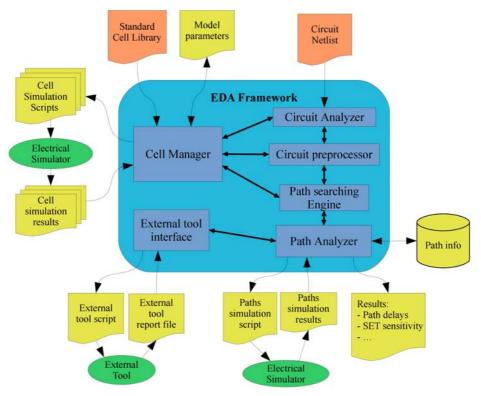

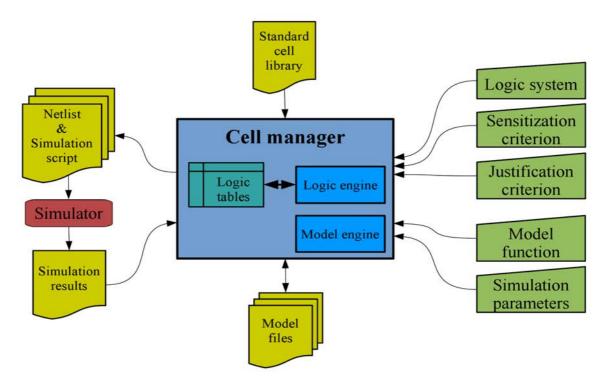

| 4.6.1.Cell manager module                                               | 103 |

| 4.6.2.Circuit analyzer                                                  | 105 |

| 4.6.3.Circuit preprocessor                                              | 105 |

| 4.6.4.Path searching engine.                                            | 105 |

| 4.6.5.Path analyzer.                                                    | 106 |

| 4.6.6.External tool interpreter                                         | 107 |

| Chapter 5: Framework application to Timing Analysis                     | 109 |

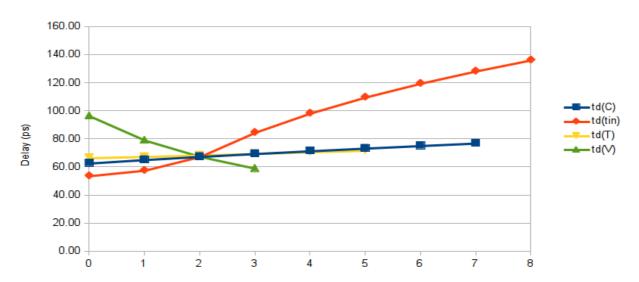

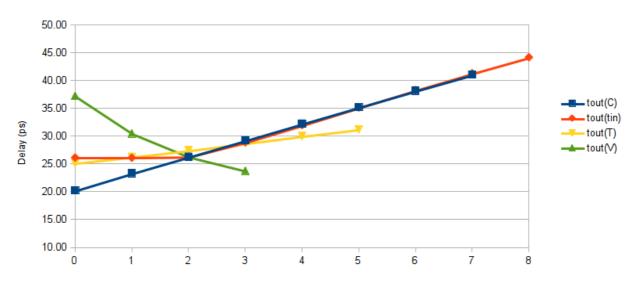

| 5.1.Polynomial Delay Model                                              | 110 |

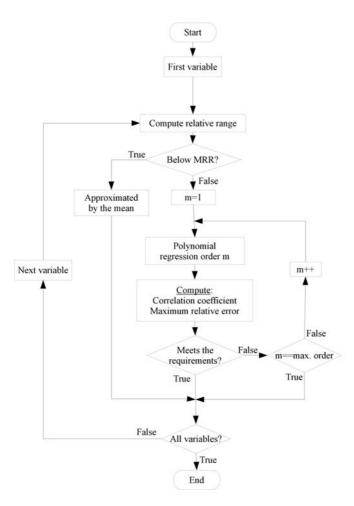

| 5.1.1.Multidimensional extraction process.                              | 113 |

| 5.1.2.Gate simulation process.                                          | 117 |

| 5.1.3.Delay model accuracy verification.                                | 121 |

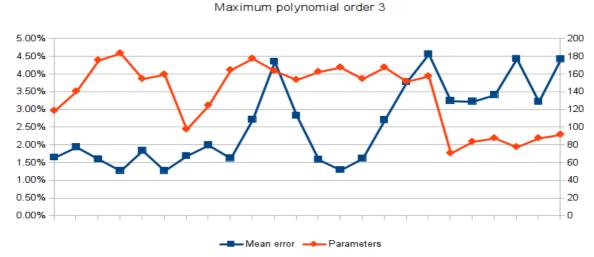

| 5.2.Effective capacitance extraction                                    | 123 |

| 5.2.1.Delay-based effective capacitance extraction                      |     |

| 5.3.Delay dependency with sensitization vector                          |     |

| 5.3.1.Gate-level analysis                                               |     |

| 5.3.2.Transistor level analysis.                                        |     |

| 5.3.3.Circuit-level relevancy                                           |     |

| 5.3.4.Sensitization vector impact on timing analysis                    |     |

| 5.3.4.1. Test circuit                                                   |     |

| 5.3.4.2. Benchmark circuits                                             |     |

| 5.3.4.3. Relevance and comparison to other effects                      | 141 |

| 5.4.Algorithms for Timing Analysis                                      | 144 |

| 5.4.1.Exhaustive path identification.                                   | 144 |

| 5.4.2. Timing estimation using path graph                               | 149 |

| 5.4.3. Timing estimation using path graph and simplification techniques | 152 |

|                                                                         |     |

| Chapter 6: Framework application to SET propagation estimation (SENSET) | 157 |

|-------------------------------------------------------------------------|-----|

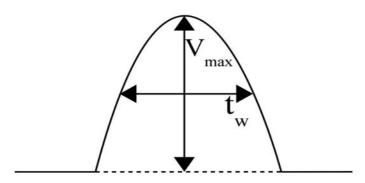

| 6.1.SET Propagation model                                               | 158 |

| 6.1.1.Model parameters extraction                                       | 159 |

| 6.2.SET Propagation Sensitivity                                         | 162 |

| 6.2.1.Logic sensitivity                                                 |     |

| 6.2.2.Electrical sensitivity                                            | 166 |

| 6.2.3.Circuit level SET sensitivity metrics                             | 167 |

| Node SET Sensitivity (NSS)                                              | 167 |

| Output SET sensitivity (OSS)                                            | 169 |

| SET Output width distribution                                           | 170 |

| 6.3.SET through reconvergence.                                          | 171 |

| 6.4.Results                                                             | 173 |

| 6.4.1.Tool Accuracy                                                     | 173 |

| 6.4.2.SENSET Analysis.                                                  | 175 |

| 6.4.2.1. Output sensitivity                                             | 175 |

| 6.4.2.2. Node SET sensitivity                                           | 179 |

| 6.4.2.3. Output width distribution.                                     | 183 |

| Chapter 7: Conclusions and future work                                  | 191 |

| References                                                              | 193 |

| A Benchmark circuits                                                    | 202 |

# **Index of Figures**

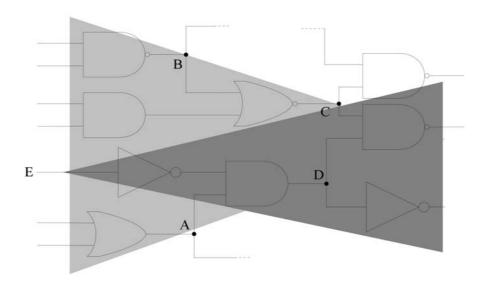

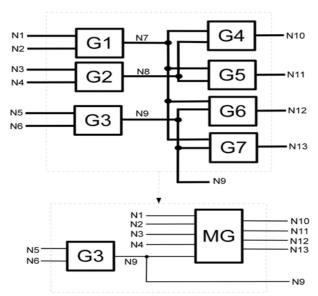

| Figure 2.1: General circuit structure                       | 6  |

|-------------------------------------------------------------|----|

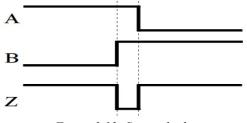

| Figure 2.2: Timing diagram                                  | 8  |

| Figure 2.3: Transition delay                                | 14 |

| Figure 2.4: Propagation delay                               |    |

| Figure 2.5: MOSFET parasitic capacitances                   | 20 |

| Figure 2.6: Inverter capacitances                           |    |

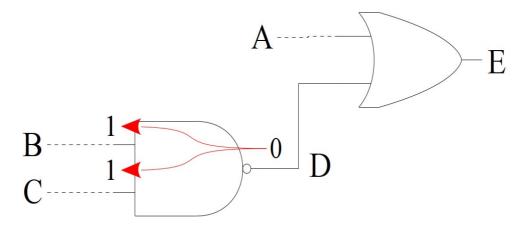

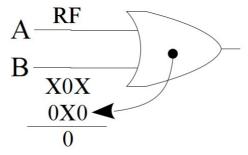

| Figure 2.7: Logic masking                                   | 25 |

| Figure 2.8: Time masking                                    | 25 |

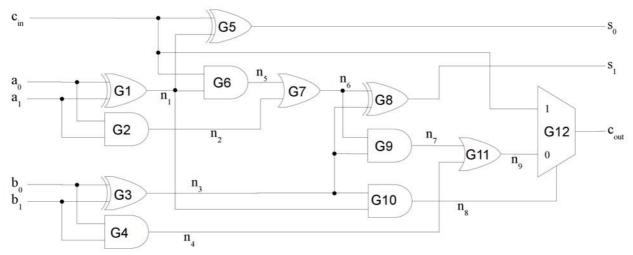

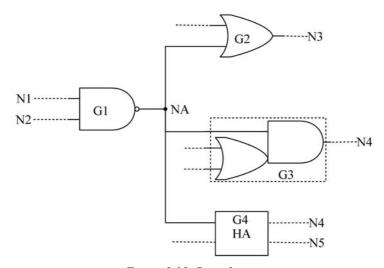

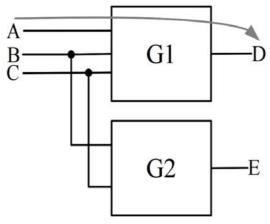

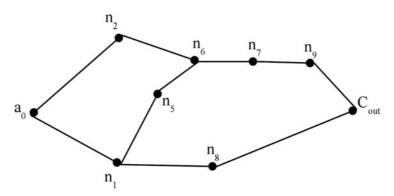

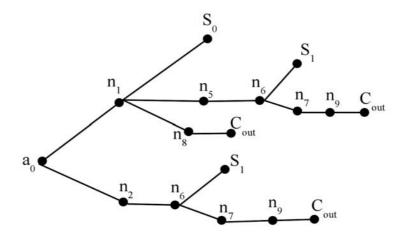

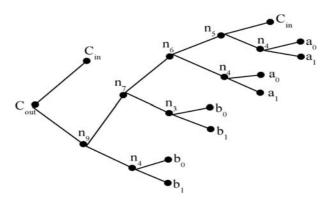

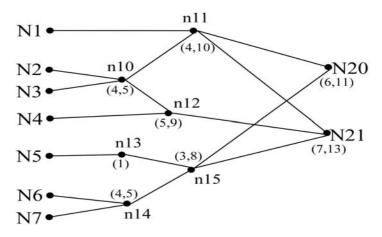

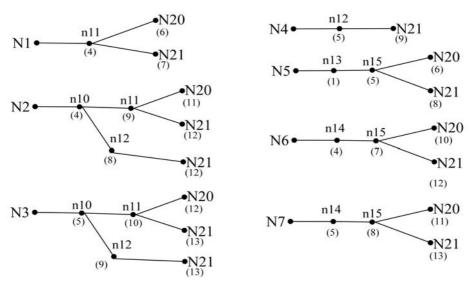

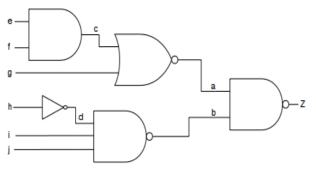

| Figure 3.1: 2-bit carry bypass adder                        | 31 |

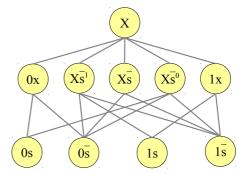

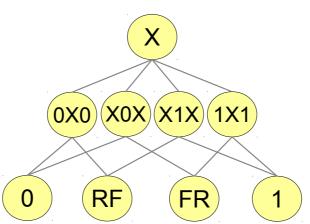

| Figure 3.2: Hasse diagram of 10-valued logic system [33]    | 34 |

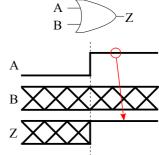

| Figure 3.3: Semi-undetermined value.                        |    |

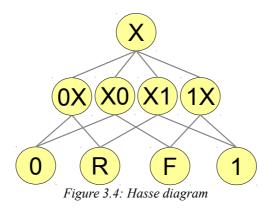

| Figure 3.4: Hasse diagram                                   | 37 |

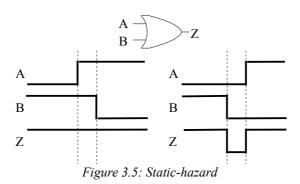

| Figure 3.5: Static-hazard                                   | 37 |

| Figure 3.6: Hasse diagram of dual value logic system        | 39 |

| Figure 3.7: Logic system example                            |    |

| Figure 3.8: Minimum sensitization conditions                |    |

| Figure 3.9: Forward implication                             |    |

| Figure 3.10: Backward implication                           |    |

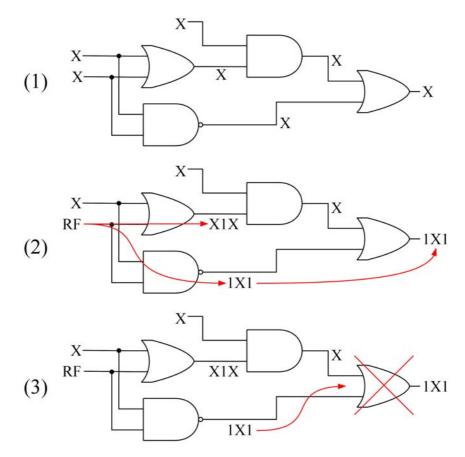

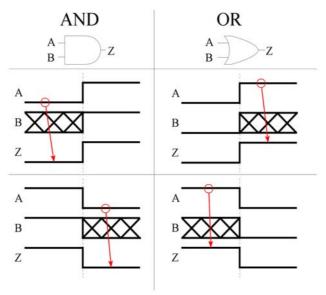

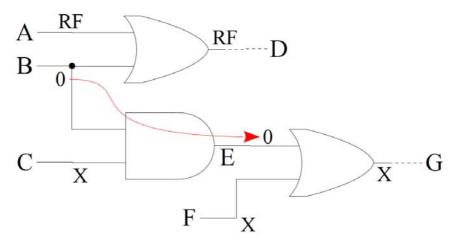

| Figure 3.11: Mixing values                                  |    |

| Figure 3.12: Static glitch                                  |    |

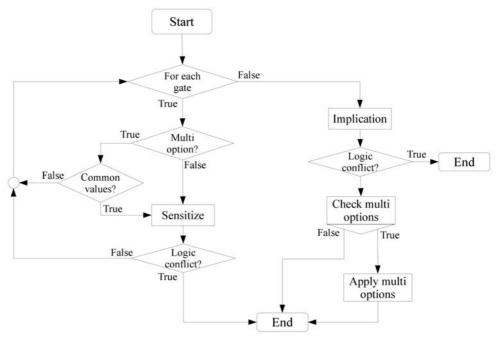

| Figure 3.13: Stepwise algorithm                             |    |

| Figure 3.14: Sensitization graph                            |    |

| Figure 3.15: Branch point                                   |    |

| Figure 3.16: Setting values                                 |    |

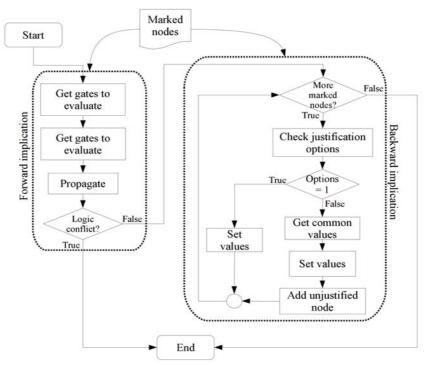

| Figure 3.17: Implication flowchart                          |    |

| Figure 3.18: Justification algorithm flowchart.             |    |

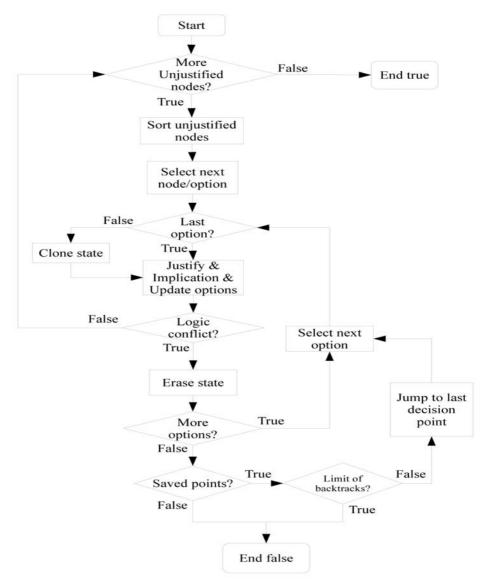

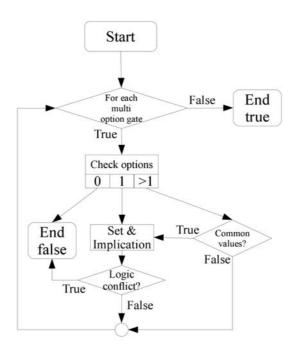

| Figure 3.19: Flowchart of full path sensitization algorithm |    |

| Figure 3.20: Full path example.                             |    |

| Figure 3.21: Flowchart of multi-option verification         |    |

| Figure 3.22: Flowchart of multi-option assignment.          |    |

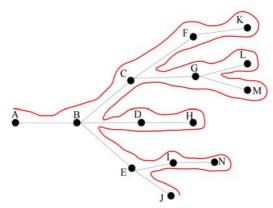

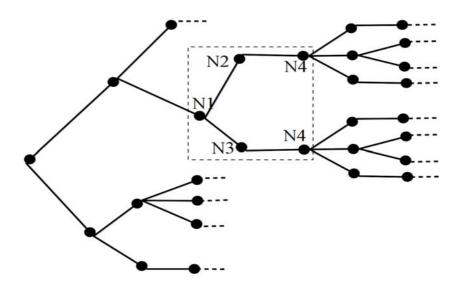

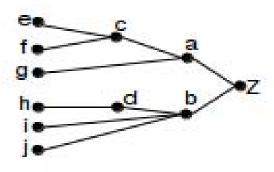

| Figure 3.23: Non-divergent In-Out graph                     |    |

| Figure 3.24: Path graph from input.                         |    |

| Figure 3.25: Path graph from output                         |    |

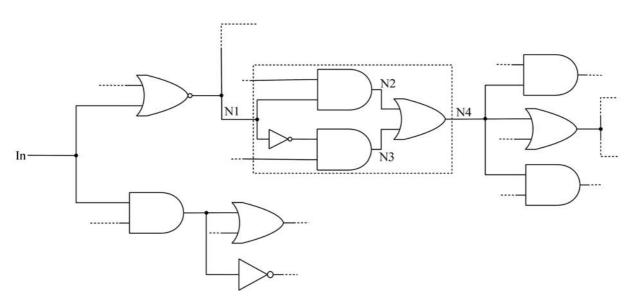

| Figure 4.1: Touch nodes algorithm                           |    |

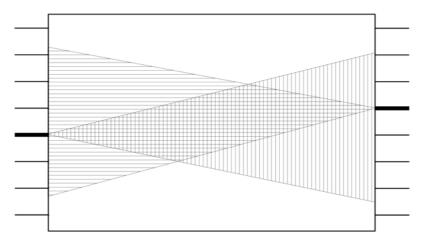

| Figure 4.2: Independent sections.                           |    |

| Figure 4.3: Partitioning by Output                          |    |

| Figure 4.4: Partitioning by input                           |    |

| Figure 4.5: Partitioning by Input-Output                    |    |

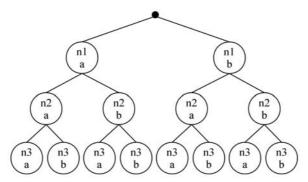

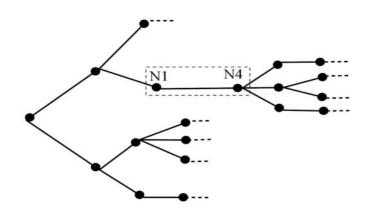

| Figure 4.6: Justification tree 1                            |    |

| Figure 4.7: Justification tree 2                            |    |

| •                                                           |    |

| Figure 4.8: Pre-sensitization.                              |    |

| Figure 4.10: Redundant inputs gets                          |    |

| Figure 4.10: Redundant inputs gate                          |    |

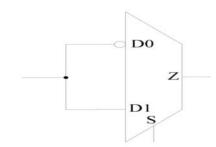

| Figure 4.11: XNOR2 implemented with a multiplexer           |    |

| Figure 4.12: Non-stem nodes                                 |    |

| Figure 4.13: Reconvergence.                                 |    |

| Figure 4.14: Single input gate                              |    |

| Figure 4.15: Shared input gates                             | 90 |

| Figure 4.16: Partially shared input nodes                       | 91  |

|-----------------------------------------------------------------|-----|

| Figure 4.17: Example circuit.                                   | 95  |

| Figure 4.18: Path graph before simplification.                  | 96  |

| Figure 4.19: Simplified path graph                              | 96  |

| Figure 4.20: General Framework Structure                        | 102 |

| Figure 4.21: Cell manager diagram                               | 104 |

| Figure 5.1: Rising input propagation delay variation            | 111 |

| Figure 5.2: Rising output transition time                       | 111 |

| Figure 5.3: Flowchart of the model extraction algorithm         | 116 |

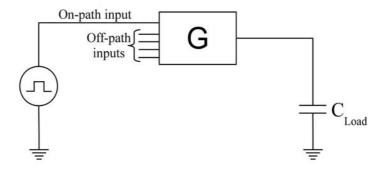

| Figure 5.4: Gate delay simulation                               | 117 |

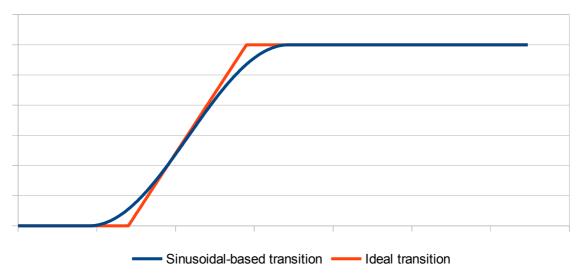

| Figure 5.5: Transition generation                               | 118 |

| Figure 5.6: Real transition.                                    | 119 |

| Figure 5.7: Mean error and number of coefficients               | 119 |

| Figure 5.8: Mean error and number of coefficients               | 120 |

| Figure 5.9: C extraction circuit.                               | 126 |

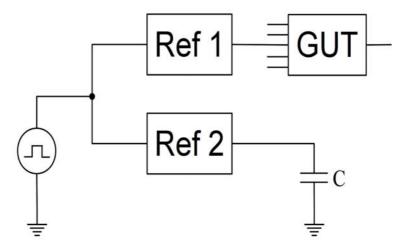

| Figure 5.10: Gate AO22.                                         | 128 |

| Figure 5.11: Gate OA12                                          | 128 |

| Figure 5.12: Gate CB4I6                                         |     |

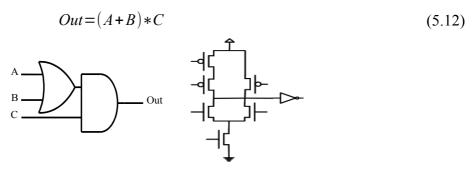

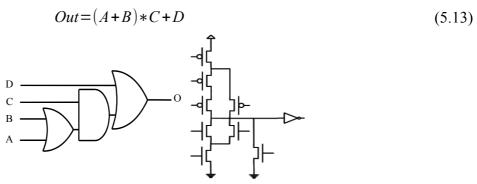

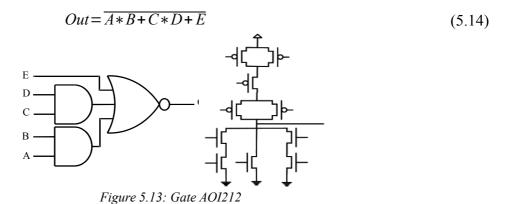

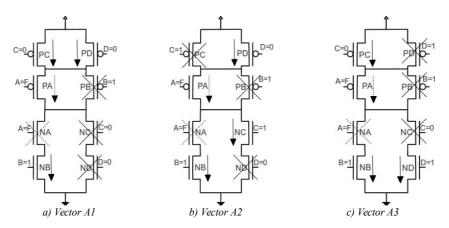

| Figure 5.13: Gate AOI212                                        | 129 |

| Figure 5.14: Gate AO22 transistor-level schematic               | 134 |

| Figure 5.15: Gate OA12 transistor-level schematic               | 134 |

| Figure 5.16: Internal currents of AO22.                         | 136 |

| Figure 5.17: Test circuit.                                      | 138 |

| Figure 5.18: Example circuit                                    | 149 |

| Figure 5.19: Circuit graph                                      | 150 |

| Figure 5.20: Path graph                                         | 151 |

| Figure 5.21: Algorithm flowchart                                | 152 |

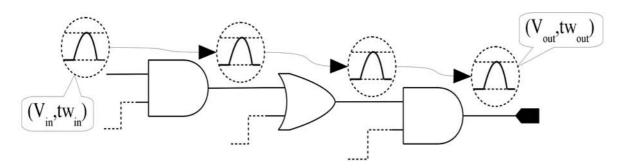

| Figure 6.1: SET pulse characteristics                           | 158 |

| Figure 6.2: SET model extraction circuit.                       | 160 |

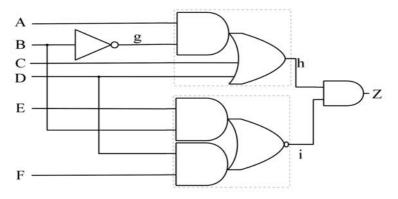

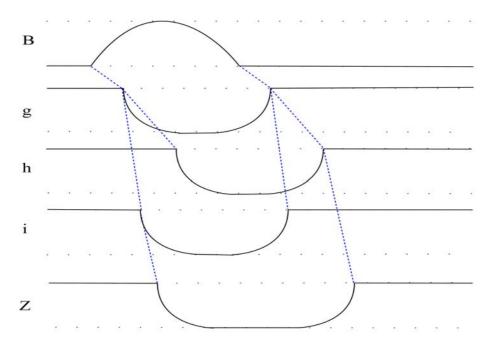

| Figure 6.3: Example circuit.                                    | 164 |

| Figure 6.4: Graph of example circuit.                           | 164 |

| Figure 6.5: Electrical propagation                              | 166 |

| Figure 6.6: Reconvergence                                       | 171 |

| Figure 6.7: SET propagation through reconvergence               | 172 |

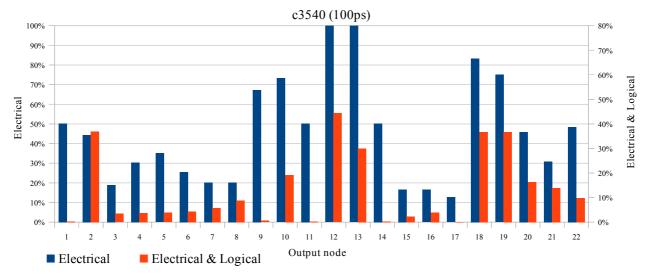

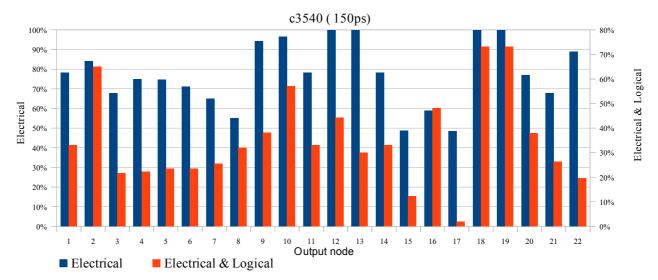

| Figure 6.8: Output sensitivity c3540 (100ps)                    |     |

| Figure 6.9: Output sensitivity c3540 (150ps)                    |     |

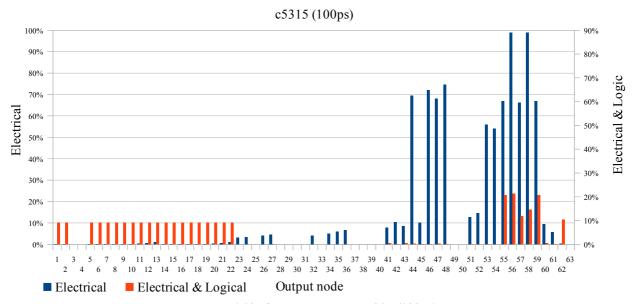

| Figure 6.10: Output sensitivity c5315 (100ps)                   | 177 |

| Figure 6.11: Output sensitivity c5315 (150ps)                   |     |

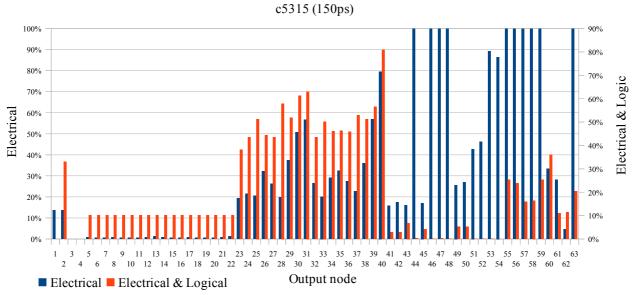

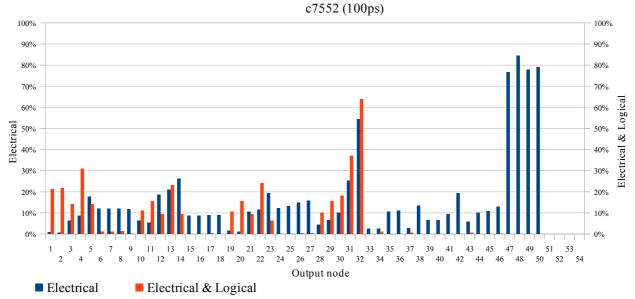

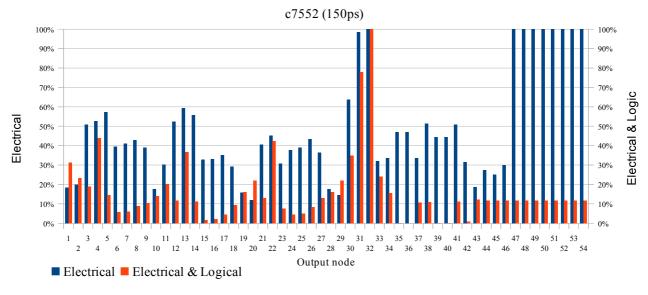

| Figure 6.12: Output sensitivity c7552 (100ps)                   |     |

| Figure 6.13: Output sensitivity c7552 (150ps)                   |     |

| Figure 6.14: c3540 Minimum pulse width                          |     |

| Figure 6.15: c5315 Minimum width                                |     |

| Figure 6.16: c7552 Minimum width                                |     |

| Figure 6.17: c3540 Minimum pulse height                         |     |

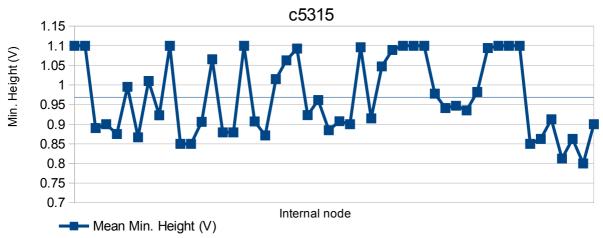

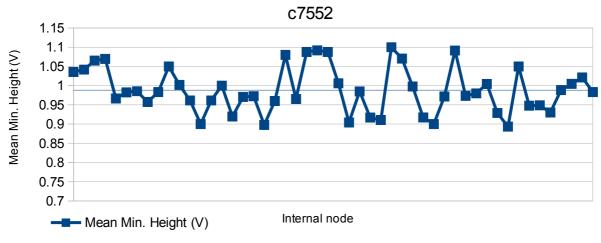

| Figure 6.18: c5315 Minimum height                               |     |

| Figure 6.19: c7552 Minimum Height                               |     |

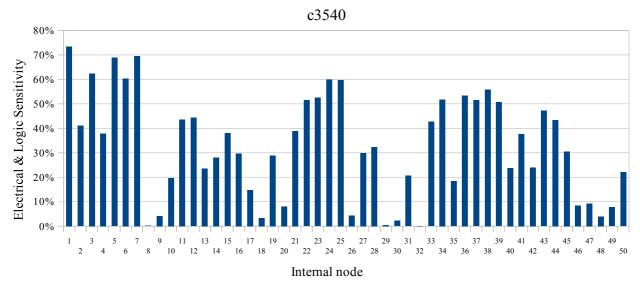

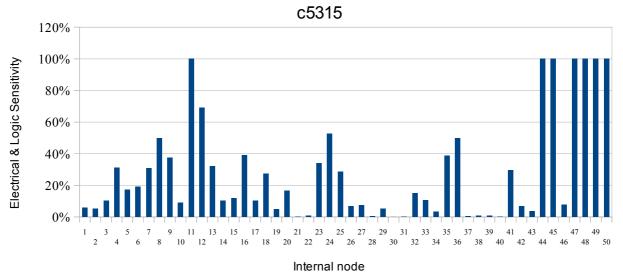

| Figure 6.20: c3540 Internal node Electrical & Logic sensitivity |     |

| Figure 6.21: c5315 Internal node Electrical & Logic sensitivity |     |

| Figure 6.22: c7552 Internal node Electrical & Logic Sensitivity |     |

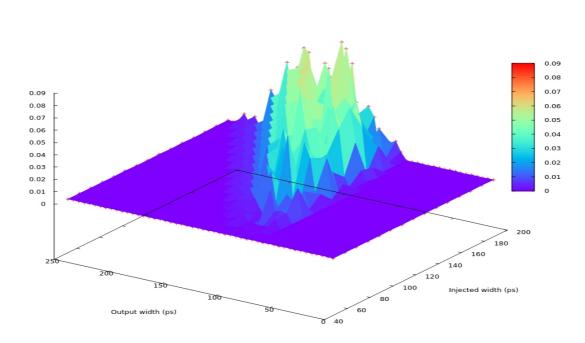

| Figure 6.23: c3540 Output width distribution (100ps)            | 184 |

| Figure 6.24: c3540 Output width distribution (150ps) | 184 |

|------------------------------------------------------|-----|

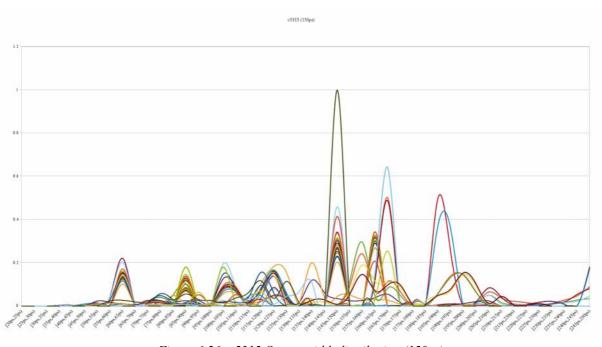

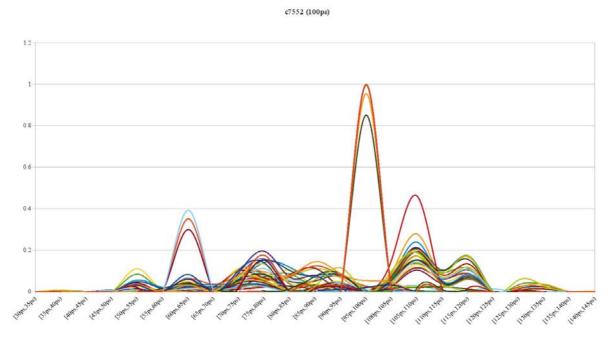

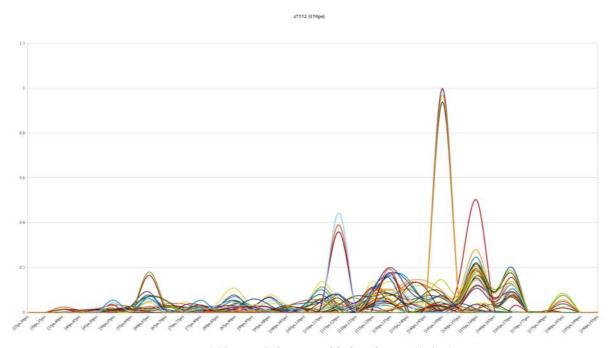

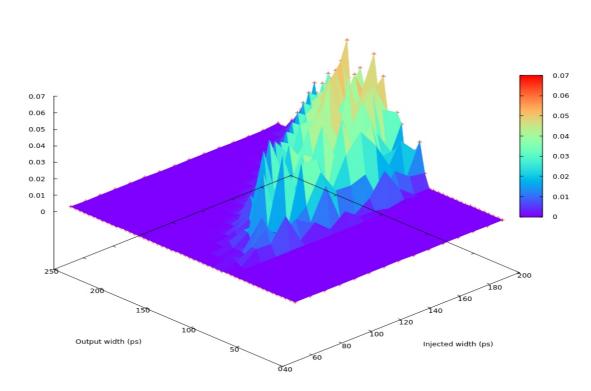

| Figure 6.25: c5315 output width distribution (100ps) | 185 |

| Figure 6.26: c5315 Output width distribution (150ps) |     |

| Figure 6.27: c7552 Output width distribution (100ps) |     |

| Figure 6.28: c7552 Output width distribution (150ps) |     |

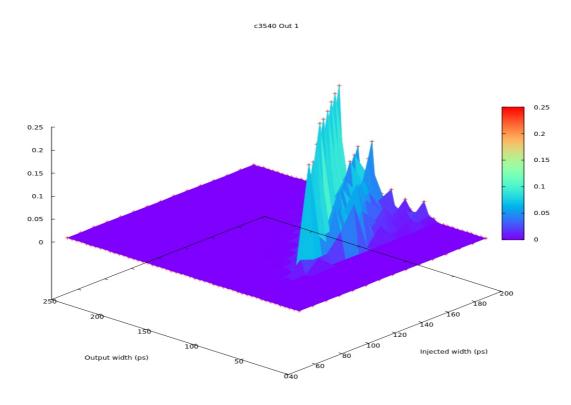

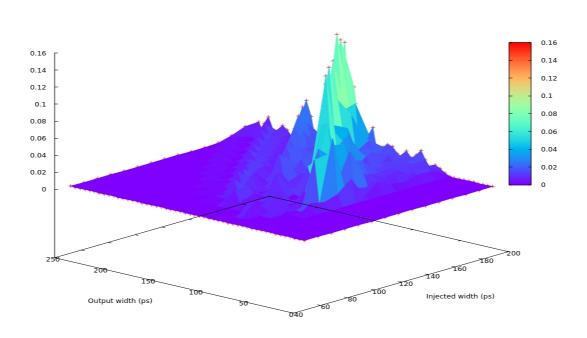

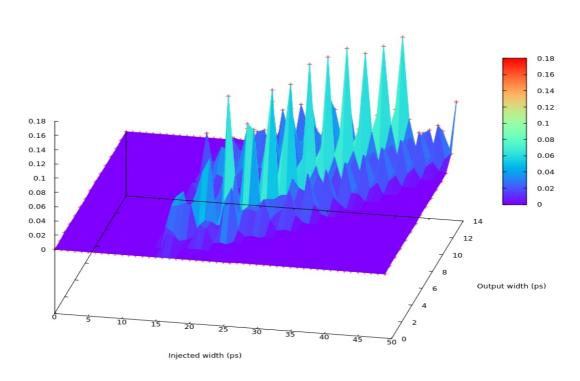

| Figure 6.29: c3540 Injected-Output width             | 187 |

| Figure 6.30: c3540 Injected-Output width             | 188 |

| Figure 6.31: c3540 Injected-Output width             | 188 |

| Figure 6.32: c3540 Injected-Output width             | 189 |

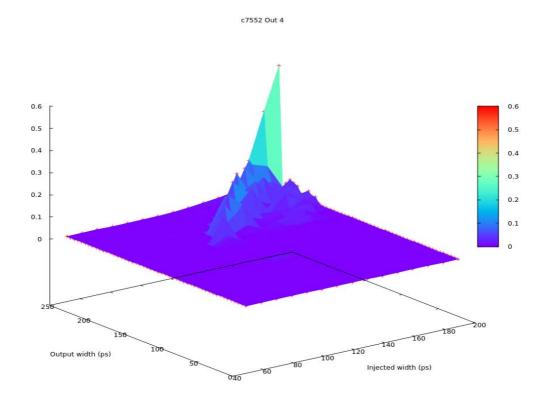

| Figure 6.33: c7552 Injected-Output width             | 189 |

| Figure 6.34: c7552 Injected-Output width             | 190 |

# **Index of Tables**

| Table 2.1: Capacitance components                                      | 21  |

|------------------------------------------------------------------------|-----|

| Table 3.1: 10-valued logic system                                      | 34  |

| Table 3.2: Initial set of values                                       | 35  |

| Table 3.3: Not gate propagation                                        | 35  |

| Table 3.4: Or Propagation                                              | 36  |

| Table 3.5: And Propagation                                             | 36  |

| Table 3.6: Dual logic system initial values                            |     |

| Table 3.7: Composite dual values                                       |     |

| Table 3.8: Minimum sensitization condition.                            |     |

| Table 3.9: Example gates                                               | 44  |

| Table 3.10: AND3 steady values sensitization                           |     |

| Table 3.11: AND3 Minimum condition sensitization                       |     |

| Table 3.12: OA12 Steady values sensitization                           | 45  |

| Table 3.13: OA12 Relaxed steady value sensitization                    |     |

| Table 3.14: OA12 Minimum condition sensitization.                      |     |

| Table 3.15: XOR2 sensitization table                                   |     |

| Table 3.16: Justification table. Steady values                         |     |

| Table 3.17: NAND2 justification options for semi-undetermined values   |     |

| Table 3.18: NAND2 justification options for transitions                |     |

| Table 3.19: Specific functions for reversible algorithm                |     |

| Table 3.20: Justification table for OA12                               |     |

| Table 3.21: Justification table for AND2 gate                          |     |

| Table 4.1: Independent sections.                                       |     |

| Table 4.2: Redundant input gates                                       |     |

| Table 4.3: Block repetition after non-stem simplification.             |     |

| Table 4.4: Block repetition examples                                   |     |

| Table 4.5: #Instances for iterative simplifications of b17             |     |

| Table 4.6: ISCAS c6288                                                 |     |

| Table 4.7: ISCAS c7552                                                 |     |

| Table 4.8: ITC'99 b17                                                  |     |

| Table 4.9: ITC'99 b20.                                                 |     |

| Table 4.10: ITC'99 b21                                                 |     |

| Table 4.11: Path graph creation.                                       | 100 |

| Table 4.12: Structural paths enumeration.                              | 101 |

| Table 5.1: Delay comparison vs electrical simulation (130nm)           |     |

| Table 5.2: Delay comparison vs electrical simulations (90nm)           |     |

| Table 5.3: Delay comparison vs electrical simulations (65nm)           |     |

| Table 5.4: RC Constant capacitance extraction.                         |     |

| Table 5.5: AO22 Propagation Table                                      |     |

| Table 5.6: OA12 Propagation Table                                      |     |

| Table 5.7: CB4I6 Propagation Table                                     |     |

| Table 5.8: AOI212 Propagation Table.                                   |     |

| Table 5.9: Propagation delay variation for AO22.                       |     |

| Table 5.10: Propagation delay variation for OA12                       |     |

| Table 5.11: Propagation delay variation for CB4I6                      |     |

| Table 5.12: Propagation delay variation for AOI212                     |     |

| Table 5.13: Circuit-level multi-sensitization impact                   |     |

| Table 5.14: Delay vs Input vector for the simple circuit in Fig. 5.17. |     |

| Table 5.15: Sensitization vector impact on critical path identification | 140 |

|-------------------------------------------------------------------------|-----|

| Table 5.16: Path delay variation.                                       |     |

| Table 5.17: Complex gates per path                                      |     |

| Table 5.18: Backtrack limit influence for ISCAS c7752                   |     |

| Table 5.19: Forward algorithm. Criterion 1                              | 146 |

| Table 5.20: Forward algorithm criterion 2                               | 146 |

| Table 5.21: Forward algorithm criterion 3                               | 146 |

| Table 5.22: Backward algorithm Criterion 1                              | 147 |

| Table 5.23: Backward algorithm Criterion 2                              | 147 |

| Table 5.24: Backward algorithm Criterion 2                              | 147 |

| Table 5.25: Forward algorithm with justification at end Criterion 1     | 148 |

| Table 5.26: Forward algorithm with justification at end Criterion 2     | 148 |

| Table 5.27: Forward algorithm with justification at end Criterion 3     | 148 |

| Table 5.28: Critical path identification (preprocessing)                | 153 |

| Table 5.29: Slowest true path identification                            | 154 |

| Table 6.1: Most sensitizable paths                                      | 174 |

| Table 6.2: Random selected paths                                        | 174 |

| Table A.1: ISCAS'85 Benchmark circuits                                  | 203 |

| Table A.2: ITC'99 Benchmark circuits                                    | 204 |

# **Chapter 1: Introduction**

With no doubt, the integrated electronic technology industry is advancing extremely fast. Even with the CMOS technology dead end predictions [1], the MOSFET transistor dimensions are shrinking each year and the number of transistors integrated within a die increases constantly [2], as was predicted by the Moore's law in 1965 [3]. This has lead to spectacular figures like some of today's commercial circuits exceeding one billion transistors integrated together in the same piece of silicon [4]. Such an evolution reduces the design margins, magnifies some side effects that were negligible in previous technologies while new adverse physical phenomena come into the picture. All these events increase the relevance of design improvement, circuit verification at multiple design stages, and testing, to ensure that a given circuit meets all operation constraints required. However, this task becomes more and more challenging due to the ever-increasing overall complexity.

Design-for-testability (DFT) is a valuable vehicle in making test complexity manageable, but even with the aid of such techniques some specific circuit verifications remain unaffordable. An advanced test and verification plan is essential given its significant economic impact on the final circuit cost. Other vital stages of the design flow are related to circuit optimization: an overall die area reduction improves the manufacturing yield reducing the cost per circuit, while power emerged as a key technology scaling restraining parameter due to thermal issues in high-end applications, and a limiting parameter of portable devices that require a very low power circuits to maximize the battery life.

One of the physical mechanisms that threaten current and future technology nodes reliability is

#### Chapter 1: Introduction

the impact of Single Event Effects (SEEs) [5]. As technology scaling reduces the circuit nodes parasitic capacitance, lowers the supply voltage and shrinks gate delay, the relative impact of ionizing particles increases because the same amount of injected charge is capable of inducing a voltage transient that may propagate within the circuit and/or induce a memory upset.

The impact of ionizing radiation on circuits behavior has been an issue deeply studied specially for circuits operating in hostile environments with high radiation levels, specially aerospace applications lacking the protection against cosmic radiation provided by the atmosphere and the earth magnetic field. Traditionally, radiation-hardening techniques were adopted almost exclusively for applications running in hostile environments. The high sensitivity to radiation of today technologies has shifted this view since commercial devices are susceptible of being affected by ionizing radiation even at sea level due to the technology miniaturization. This trend is motivating the adoption of procedures to consider the soft-error susceptibility caused by particle impacts within the design flow of current consumer electronic circuits.

The main impact of soft-errors caused by ionizing particles affected traditionally circuit memory subsystems. The adoption of circuit redundancy and error correction codes (ECC) for critical memory systems has accomplished maintaining the soft-error rate (SER) associated to memory elements within tolerable limits despite the technology evolution. However, the SER associated to the combinational logic has experimented a considerable increase with technology scaling, since their impact is favored by such scaling.

Apart of redundancy-based techniques, many mitigation solutions are based on increasing the circuit intrinsic robustness to SEEs. Although these strategies cannot avoid the problem completely, they reduce the soft-error impact to an acceptable limit that depends on the final application.

# 1.1. Motivation and objectives

The growing impact of transient effects caused by radiation phenomena in combinational circuits has motivated an increasing interest in the development of efficient Single Event Transients (SET) description and mitigation techniques. Although the basic mechanisms governing SET propagation within combinational blocs have been extensively studied and are well known, the development of efficient propagation models suitable for nanometer technologies is of enormous interest nowadays. SET modeling has an inherent difficulty related to the complexity of describing the propagation of a non-purely digital perturbation within large or complex digital blocs where electrical-level

descriptions are not suitable. SET propagation descriptions must accomplish various conditions for them to be efficiently adopted as valid descriptions in industrial environments [6] including accuracy, compactness and simplicity.

However, although efficient compact models are available [7], their adoption by the research community is conditioned to their practical application within circuit-level analysis in an affordable way. In this context, the development of efficient EDA tools capable of covering the gap between the gate level model verification – typically accomplished through electrical-level simulations not suitable for large blocks – and the realistic complex circuit domain is lacking. Such a framework is capital to advance in the overall application and evaluation of SET mitigation techniques, as they require quick and efficient ways of evaluating various circuit alternatives, as well as being capable of determining the best option between different solutions.

Such achievement is complex since it is not a merely implementation of a given analytical model within a tool given the complexity of today IC designs. A practical solution requires an efficient implementation of a complete framework capable of tracing true paths within a circuit, accurately accounting for the propagation delay, efficiently managing complex circuits and providing a powerful information about circuit SET sensitivity according to various design abstraction levels.

The creation of such a framework is the focus of the work developed in this thesis, exploiting the benefits of compact modeling descriptions developed within the research group where this thesis has been developed. Although the main objective is focused on developing specific SET propagation analysis tools, when integrating such components within existing commercial tools, secondary objectives have been found as the work has been carried over. The low efficiency and low accuracy of some commercial tool modules have motivated the development of specific framework elements oriented to efficiently computing standard tasks like efficient true path enumeration, efficient gate and path delay computation and efficient handling of highly complex circuits.

The final objective is to provide the circuit designer with a valuable tool to analyze the circuit SET sensitivity in terms of SET propagation for various design abstraction levels. The framework must be capable of being used either by gate-level design and/or synthesis applications as well as by block-level integration designers and tools. In this way, the framework must be capable of providing in-circuit information by grading internal nodes in terms of their SET sensitivity, as well as detailing block-level analysis when treating the circuit as a box.

#### Chapter 1: Introduction

Following the established tool evaluation methods, the framework is aimed to be validated through electrical-level simulations applied through standardized benchmark circuits synthesized on a wide set of commercial and open-source technologies. Application on large benchmark circuits will allow evaluating the framework capabilities compared to "de facto" standardized commercial tools.

# 1.2. Document organization

This work is divided in seven chapters organized as follows:

Chapter 2 provides a general view of the main topics covered in this thesis. It introduces basic concepts about timing analysis and SET propagation through a combinational circuit, and some theoretical foundations relative to analytical modeling techniques and logic gates capacitances.

In chapters 3 and 4 are detailed the algorithms and techniques included in the framework for combinational circuits processing.

Chapter 3 is focused on identifying paths capable to propagate a transition through a combinational logic block. It starts by defining the basic concepts about paths through a circuit and then explains the new logic system developed for true path identification. The algorithms for path identification are described step by step detailing each individual task.

Chapter 4 presents solutions for the limitations of the algorithms of chapter 3 when are applied to very large circuits, and explains a set of circuit simplification techniques to reduce the circuit complexity allowing to process complex circuit design in a reasonable time.

In chapters 5 and 6 show the application of the framework developed to solve two key tasks for a proper design flow of a reliable digital circuit.

Chapter 5 presents an analytical delay model based on the mathematical concepts introduced in Chapter 2, and its application in combination with the path identification techniques to timing analysis.

Chapter 6 presents how the framework components are applied in combination with an analytical SET propagation model to estimate the SET propagation capability of a combinational circuit providing SET propagation sensitivity metrics. This metrics may help to improve the designs tolerance to radiation induced effects.

Finally, chapter 7 exposes the conclusions drawn from this work and the future work.

# Chapter 2: Timing analysis and SET propagation

This chapter provides a global insight of basic concepts discussed in detail in the following chapters, with the objective of establishing the foundations of the work developed in this thesis. The chapter starts presenting the essential concepts related to timing analysis being a key step in the design of a synchronous digital circuit. It follows with the mathematical theory on which the analytical modeling technique implementation used in this work is based. Finally the basics about the SET propagation through a combination block are introduced.

# 2.1. Timing analysis

Timing analysis is a key step in the design flow of synchronous digital circuits, validating the proper timing performance of a circuit design [8]. Its significance and complexity increases with technology scaling due to new physical phenomena appearing in nanometer technologies [9][10] and the increase in integration density.

A synchronous digital circuit is intended to operate at a given clock rate and timing analysis is responsible to verify if the combinational blocks delays meet the timing constraints imposed by the system clock frequency and the characteristics of sequential elements. Theoretically, such timing constraints can be verified through a detailed circuit simulation, but such simulation are too slow that in practice remain completely unaffordable for large circuit designs due to their excessive computational resources requirements. Therefore the timing analysis is performed using simplified delay models seeking a balance between accuracy and computation time.

#### Chapter 2: Timing analysis and SET propagation

Circuit synthesis is performed according to multiple constraints set by the designer like area, power and timing. Timing analysis is used to guide the synthesis selecting the proper logic gates to implement the expected logic function accomplishing the design constraints. However, timing constraints remains among the most important design constraint since if they are not meet, the circuit is unable to operate correctly at intended clock frequency.

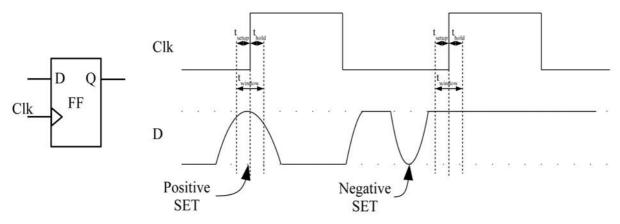

The timing analysis objective during the design flow is to ensure that the correct logic value will be present at the data input of each sequential element when the clock edge arrives, allowing that the memory elements capture the correct logic values.

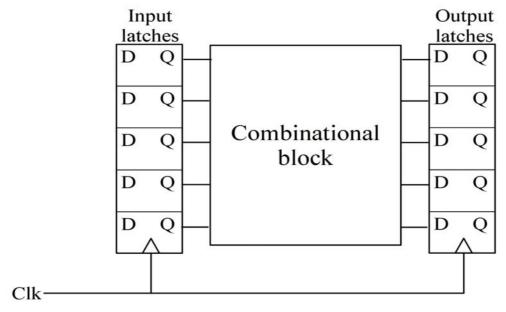

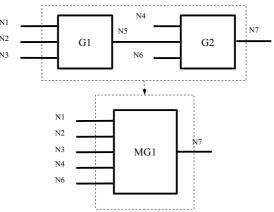

Fig. 2.1 shows a generic structure of a sequential circuit where a combinational logic block is located between two sets of latching elements, the input latches and the output latches, both controlled by a clock signal (*Clk*). Input latches apply a logic vector at the combinational block inputs keeping these values stable during one clock cycle. Output latches capture the logic values arriving at the block outputs, their outputs constitute the inputs to the following combinational block (not shown in the Figure). To guarantee correct circuit operation, the circuit response to an input vector at a given clock edge must provide valid stable values at data input of the output latches before the next clock edge arrives.

Figure 2.1: General circuit structure

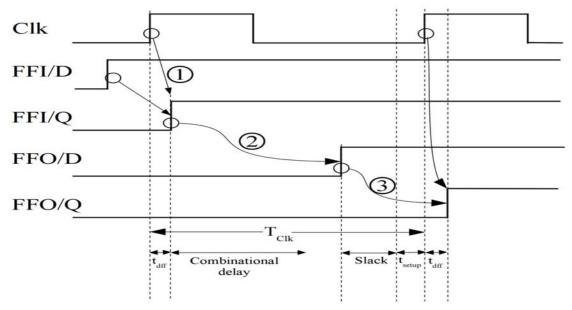

Fig. 2.2 shows a timing diagram to illustrate the circuit operation. FFI is one of the input latches and FFO is an output latch.  $T_{Clk}$  is the clock period, i.e. time interval between two consecutive clock

edges, therefore the operating frequency is  $f = \frac{1}{T_{C/k}}$ .

The sequence of events represented in Fig. 2 can be divided in three steps as follow:

- (1) A clock edge arrival latches the data at the input D of the FFI (FFI/D) placing the captured data at its output Q (FFI/Q). The time required by a latch to set the captured value at the output Q after the triggering clock edge is denoted as t<sub>dff</sub>, i.e. the delay of the memory element. The time instant at which the data is placed at the inputs of the combinational block is referred as *launch time*.

- (2) Once the logic values are stable at the inputs of the combinational block at *launch time*, the change is propagated through the logic until the outputs of the combinational block. The *arrival time* is the time instant at which the outputs of the combinational block take the correct logic value. The difference between *arrival time* and the *launch time* is the delay of the combinational logic block.

- (3) The next clock edge triggers the capture of the output values, however the latches require that the data to be captured be stable at input D before the clock edge arrival. The amount of time the data must be stable before the clock edge arrival is called *setup time* (t<sub>setup</sub>) and depends on the specific latch characteristics. Correct data must be stable at the data input of the latches the *setup time* before the clock edge, this instant is referred as *required time*, i.e. is the instant at which the correct logic must show up at the combinational block outputs for proper operation. After the clock edge the data must remain stable at the inputs of the latches an amount of time called *hold time* (t<sub>hold</sub>) to be properly captured.

Figure 2.2: Timing diagram

The time between the *arrival time* and the *required time* is called *slack* (2.1), this is the amount of time by which the timing constraint is met.

$$slack = required time - arrival time$$

(2.1)

If the *slack* is positive, as shows the example of Fig. 2.2, then the signal arrives earlier than the *required time*, and therefore timing constraint is met. However if the *slack* is negative then the signal arrives later than the *required time*, producing a timing constraint violation. If the *slack* is exactly zero then the timing constraint is theoretically met, however in the practice the *slack* must be greater than zero to ensure the proper operation, accounting for parameter variations and timing inaccuracies.

This type of timing check is referred as setup time check, although it is not the unique timing check performed by a timing analysis tool. Timing checks usually performed during the timing analysis are:

- Setup time check: Verifies that the data arrives soon enough before the clock edge to be correctly captured, i.e. the signal is stable at the outputs before the *required time*. This is the most common type of timing analysis, involving the longer paths though the combinational block that determines the larger propagation delays.

- Hold time check: Verifies that the data remains valid enough time to satisfy the *hold time* of the latches. This type of analysis involves the shortest paths through the logic ensuring that

the data does not change too early.

Hold time violation verification is mandatory to ensure the correct circuit operation, since a hold time violation may cause a circuit malfunction due to a corrupt data captured by an output latch. This type of timing violations involves exclusively the shortest paths through a combinational block and therefore do not impose any restriction on the circuit operating frequency. Therefore, hold time violations are easy to identify and solve since they can be only caused by extremely short paths and are easily solved by adding a buffer or increasing the delay of some path gate causing the violation. For this reason, out attention will be concentrated on the setup time check.

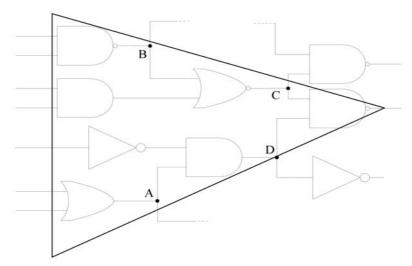

Setup time checking is quite more complex than hold time checking since it requires identifying the largest propagation delay through the combinational block, involving the concept of critical path [11]. The critical path is defined as the path from an input node to an output node of a combinational logic block having the maximum delay [12]. The critical path delay determines the circuit maximum operating frequency.

The simplest way to estimate the maximum delay through a combinational logic block is to take the longest topological path computed by assigning a delay value to each gate in the circuit and adding the delay of the gates traversed by a path. This is a quick way of identifying the largest delay through a logic block, and may be useful as a first approximation to the maximum operating frequency permitted. However, in many cases the largest topological path is a false path being non-sensitizable meaning that a transition can never be propagated through this path. Consequently a maximum circuit delay overestimation may lead to a pessimistic timing analysis [13].

The path really determining the maximum block delay is the longest true path that in some cases may be considerably shorter than the longest topological path, since all longest paths may be false. Identification of the longest true path allows performing a more accurate timing analysis. This may allow increasing the operating frequency or keeping the frequency and reducing the circuit area and power consumption thanks to the use of weaker gates, i.e. logic gates with lower conductance having worst delay and consequently requiring less area and power consumption.

A pessimistic timing analysis occurs when the path considered to be critical is really a false path slower than the longest true path. This overestimates the maximum delay, although the correct circuit operation is guaranteed. Otherwise, if the worst true path is not correctly identified, and the path considered critical is not really the slowest true path an underestimation of the maximum delay is obtained. This corresponds to an optimistic timing estimation and may give rise to a circuit

#### Chapter 2: Timing analysis and SET propagation

malfunction. Thus, the correct identification of the critical path through a combinational block is a key step to perform a precise timing analysis.

A proper timing analysis must ensure that the circuit meets the timing constraints under different conditions and therefore must consider delays variations. Since the delay through a given path depends on multiple factors, then the circuit critical path may change depending on these factors. The elements that impact the delay through a path can be divided in two categories depending on its nature:

#### Internal:

- Parameter variations

- Aging

- o In-circuit Noise

#### External

- Temperature

- Supply voltage

- External perturbations

The internal factors are specific of each circuit sample and operation, while the external factors depend on the operating environment conditions. Parameter variations occur between samples of the same circuit design due to imperfections of the manufacturing process, and are a static factor since they do not change over time. There are two types of parameter variations:

- Die-to-die: The physical parameters of the devices, like dimensions or doping levels, vary between two samples of the same circuit even when are manufactured by the same process.

- Intra-die: Different regions of a single circuit suffer different parameter deviations in addition to the die-to-die variations. Intra- or within-die variations are due to the statistical nature of some manufacturing steps.

Circuit aging, is a degradation of the circuit components that in general worsens the circuit performance unlike the parameter variation that may produce circuits faster than the mean. In general, aging affects differently each circuit sample, since it depends strongly on factors like operating temperature since many aging effects involves thermally activated physical mechanisms [14][15]. However, despite its time dependent nature the aging in general affects the circuit slowly, requiring a long period of operation to experience important circuit performance degradation, specially compared to the external factors that present a very dynamic behavior [16].

Noise mechanisms may couple internal circuit nodes or induce supply/ground fluctuations that are highly operation dependent. Noise mechanisms like capacitive and inductive coupling are physically well understood and in theory could be accurately described and their influence on delay is highly dependent on the circuit operation. Circuit complexity and the dependence of such mechanisms on circuit operation prevent a practical description of these mechanisms that in practice are modeled as random in nature, adding to parameter variations [17].

The external delay variations factors are very dynamic as they can vary considerably during the circuit operation in short periods of time. The supply voltage should be stable in general however in addition to circuit activity there may be external effects that cause voltage drop effect. The voltage drop can affect the entire circuit or be localized to specific regions. Beside the unwanted effects, in modern circuits the supply voltage is intentionally lowered depending on the circuit activity to reduce power consumption and heating. Temperature is also a highly dynamic factor that depends on the environment temperature, the heat generated by the circuit itself and the cooling mechanisms to dissipate this heat.

All factors together contribute to variations in the propagation delays through a circuit that are different from one sample of the circuit to another and depending on the environment conditions and the circuit activity.

In summary, timing analysis must verify that the circuit meets the timing constraints in the worst case conditions, at least for the range of operating conditions imposed to the design. Depending on the way to consider the variations there are two types of timing analysis:

STA (Static Timing Analysis): Computes the delays in a deterministic way i.e. considering static conditions. Possible variations on the static conditions are accounted by simulating

#### Chapter 2: Timing analysis and SET propagation

multiple sets of conditions. Usually the STA uses a strategy called corner analysis that provides a conservative result since corners settings are sets of extreme conditions. Therefore corner analysis guarantees the proper operation of the circuit under the worst possible conditions although this leads to a pessimistic analysis. The situation where all variables take the worst possible value for all components of the circuit is very unlikely.

• SSTA (Statistical Static Timing Analysis): Computes the delays through a circuit using probability distributions instead of deterministic values, giving a distribution of possible circuit outcomes rather than a single value. In general SSTA provides a less pessimistic prediction than the corner analysis at the cost of more complex process and larger runtime. The increase of parameter variations has motivated a considerable growth of this research field.

Independently of the strategy chosen and the variables considered, an accurate timing analysis requires the ability of identifying the set of true paths suitable of becoming a critical depending on the operating conditions. The importance of critical path identification relies on the fact that the delay difference from one path to another may be larger than the variation produced by the operating conditions and parameter variations. Thus this work is focused on precise path identification.

# 2.2. Delay modeling

The propagation delay through a combinational circuit determines the maximum frequency of operation of this circuit since the output signals must be correct and stable when the output memory element captures this value. If the propagation delay of a path is larger than the clock cycle, then the memory element will most probably capture an incorrect value [18]. These kinds of errors are called delay faults, and may be difficult to identify during the design stage [19].

To ensure that a circuit design will operate at a designated frequency, or to estimate the maximum frequency at which it could operate, a timing analysis of the design is required. This analysis must be performed during the design stage before manufacturing given the costs associated to an incorrect timing operation. Electrical simulation of complete real circuits is unaffordable due to the excessive computation resources required. This is solved through delay models that sacrifice accuracy to gain in computational speed. Some published delay models work at the transistor-level allowing their application to full custom designs and usually requires complex modeling techniques. Since many designs are completed through a synthesis process based on standard cell libraries, the delay model used in this Thesis works at the standard cell level.

Before introducing the mathematical details of the model and the algorithms to extract the required parameters, some well-known basic definitions about cell-level delays are detailed.

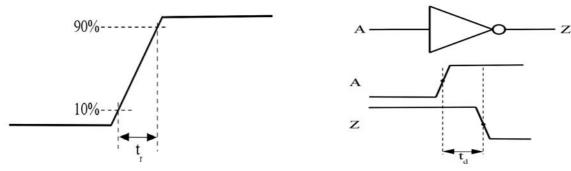

Definition: The <u>propagation delay</u> of a gate in a digital circuit is the time required by a signal to pass through the gate from one input to its output. This delay is given as the time lapse between the instant at which the input transition crosses the 50% of the supply voltage, and when the output transition crosses the same point, independently of the transitions direction. Fig. 2.4 shows a representation of the propagation delay through an inverter.

Definition: The <u>transition time</u> or slew time, is time required to change the voltage of a signal from its initial to its final value. The transition time is measured as the time between the instants when the signal crosses the 10% and the 90% of the supply voltage, for a rising transition and the opposite for a falling transition. Fig. 2.3 depicts a rising transition and its transition time.

#### Chapter 2: Timing analysis and SET propagation

Figure 2.3: Transition delay

Figure 2.4: Propagation delay

#### 2.2.1. Empirical modeling

Physically based delay models are derived more or less directly from the equations governing the voltage and current expressions that describe logic gate transitions. Technology scaling increases the transistor current expressions complexity as the device is miniaturized due to the side effects impacting its behavior. Such a complexity increase has an impact on physically based delay models whose growth makes them difficult to handle [20]. One alternative to overcome the high complexity of models based on physical descriptions is the use of empirical models extracted directly from the circuit behavior instead of its physical principles. Various alternatives have been proposed as exposed next.

#### 2.2.1.1. *Lookup Table (LUT)*

A widely used strategy is the Lookup table (LUT) that involves tabulating a set of values for the magnitude of interest. Each value correspond to a combination of the considered variables, thus, the dimensionality of the table depends on the number of variables considered. In this approach, the data is discrete and the magnitude of interest is known for a discrete set of the input variables values. The result for any other value is obtained through interpolation algorithms that may range from a simple lineal interpolation to more complex interpolations techniques. This is equivalent to having piecewise model with a function that depends on the interpolation algorithm used. Despite all the benefits of LUT techniques, an analytical model has some advantages over LUT. Depending on the model analytical expression, the computation time may be faster than the interpolations required by LUT methods. The memory space required to store the model data is in general much smaller for analytical models and depends on the LUT size compared to the number of parameters of the analytical model. To accomplish the same accuracy through both methods, the LUT must have a considerable size resulting in a larger memory requirement. However, the main advantage of

an analytical model is the capability of being mathematically manipulated as for example differentiated, providing a measure of the impact of a fluctuation on a given variable.

Various analytical methods are typically used to model any magnitude with any number of variables. Some of them are detailed next.

#### 2.2.1.2. Polynomial model

As was stated in 1712 by the Britannic mathematician Brook Taylor, any differentiable function can be represented by an infinite sum of terms that are calculated from the values of the function's derivatives at a single point. If the infinite series is truncated in a finite order, the result is an approximation of the function in some neighborhood. The order where the series is truncated determines the approximation to the real function. The Taylor series may be compactly written as (2.2)

$$f(x+x_0) = \sum_{n=0}^{\infty} \frac{f^{(n)}(x_0)}{n!} \cdot x^n$$

(2.2)

A more practical representation of the polynomial function is given by (2.3).

$$y = f(x) = \sum_{i=0}^{n} P_i \cdot x^i$$

(2.3)

Equation (2.4) shows the equivalence between the polynomial parameters and the Taylor series terms.

$$P_{i} = \frac{f^{(i)}(0)}{i!} : 0 \le i \le n \tag{2.4}$$

To model some physical magnitude using this analytical expression, the parameters of the polynomial  $(P_i)$  must be extracted from the empirical data, or in the specific case of the digital circuit analysis, from electrical-level simulations results. A great advantage of the polynomial approach is that it does not require a numerical process to fit the data to the function. Instead, the parameters can be computed analytically, using a linear systems solver for which very efficient computation algorithms exists.

#### 2.2.2. Extraction process

Starting with a set of empirical data (y) regarding to one variable (x), as shows (2.5), a polynomial regression of order n, can be accomplished by solving a linear system represented by the matrix equation (2.6).

$$y = f(x) \tag{2.5}$$

$$\underline{\underline{A}}_{(n+1)x(n+1)} \cdot \underline{P}_{(n+1)} = \underline{B}_{(n+1)} \tag{2.6}$$

Below are the details about the matrix A and both vectors P and B of (2.6). As shown in (2.7), matrix A is formed by sums of powers of the values of the independent variable x. The elements of vector P are directly the polynomial coefficients we are searching for. Vector B contains sums of products between the values of the dependent variable y, and powers of the independent variable x.

$$\underline{\underline{A}}_{(n+1)x(n+1)} = \{a_{ij}\} : a_{ij} = \sum_{k=0}^{m-1} x_k^{(i+j)}$$

$$\underline{\underline{P}}_{(n+1)} = \{p_i\}$$

$$\underline{\underline{B}}_{(n+1)} = \{b_i\} : b_i = \sum_{k=0}^{m-1} x_k^i \cdot y_k$$

$$\forall 0 \le i, j \le n+1$$

(2.7)

Where m is the number of samples of the data to be adjusted, and n is the order of the polynomial. I.e., the maximum polynomial expression exponent since the first exponent is 0, and the number of coefficients is n+1. An extended representation of matrix A, and vectors P and B are shown below.

$$\underline{\underline{A}}_{(n+1)x(n+1)} = \begin{bmatrix} m & \sum x_{i} & \sum x_{i}^{2} & \cdots & \sum x_{i}^{n} \\ \sum x_{i} & \sum x_{i}^{2} & \sum x_{i}^{3} & \cdots & \sum x_{i}^{n+1} \\ \sum x_{i}^{2} & \sum x_{i}^{3} & \sum x_{i}^{4} & \cdots & \sum x_{i}^{n+2} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \sum x_{i}^{n} & \sum x_{i}^{n+1} & \sum x_{i}^{n+2} & \cdots & x_{i}^{2n} \end{bmatrix} \quad \underline{\underline{P}}_{n+1} = \begin{bmatrix} p_{0} \\ p_{1} \\ \vdots \\ p_{n} \end{bmatrix} \quad \underline{\underline{B}}_{n+1} = \begin{bmatrix} \sum y_{i} \\ \sum x_{i} y_{i} \\ \sum x_{i}^{2} y_{i} \\ \vdots \\ \sum x_{i}^{n} y_{i} \end{bmatrix}$$

$$(2.8)$$

The order of the polynomial that must be used depends on two factors, the specific form of the data to adjust, and the accuracy desired.

#### 2.2.3. Multivariable polynomial model

So far we have only considered one variable, while modeling the behavior of a circuit, in general, requires multiple variables. To include more variables into the model, the polynomial regression can be used hierarchically, i.e., each parameter of the polynomial is a function of another variable, which can also be adjusted to a polynomial form, and so on. As an example, (2.9) shows a function of two variables (x and y) fitted to a polynomial expression regarding to variable x, where each coefficient  $P_i$  is a function of y.

$$f(x,y) = \sum_{i=0}^{n_x} P_i(y) \cdot x^i$$

(2.9)

As shown in (2.10), each  $P_i$  coefficient is also expressed as a polynomial. The order of the polynomials  $(n_x, n_{y_i}: 0 \le i \le n_x)$  may be different for each case depending of the specific characteristics of each function. Finally (2.11) gives the general expression for 2-variable function fitted to a polynomial expression. This expression for two variables can be easily generalized to any number of variables.

$$P_{i}(y) = \sum_{j=0}^{n_{y_{i}}} P_{ij} \cdot y^{j} \quad \forall P_{i} : 0 \le i \le n_{x}$$

(2.10)

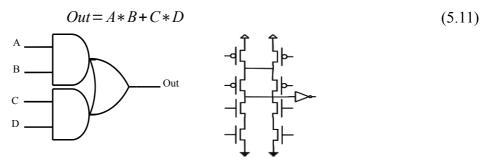

$$f(x,y) = \sum_{i=0}^{n_x} \sum_{j=0}^{n_{y_i}} P_{ij} \cdot x^i \cdot y^j$$

(2.11)

To extract the coefficients for a multivariable model, the process is the same than the one explained for a single variable, simply applying it with respect to the first variable for each value of the second variable, resulting in a set of coefficients for each value of the second variable. In the second step these coefficients are fitted with respect to the second variable, obtaining a set of coefficients for each coefficient of the first step, and so on if there are more than two variables. The final result is a matrix of coefficients, with a number of dimensions equal to the number of variables. Depending on the order used for each regression some elements of this matrix can be null.

#### 2.2.4. Computational advantages

The multi-variable polynomial model provides some computational advantages. The model coefficients can be represented using a matrix, with as much dimensions as variables considered. Since the matrix algebra has a wide use in the data processing field, this method benefits from the advances in the matrix computation. There are highly efficient matrix algorithms and even libraries that offer parallel computing to exploit current multi-core processors capabilities.

This kind of model allows performing a partial pre-computation by assigning a constant value to any of the considered variables. For instance, if the model depends on n variables, but in a specific application some of them have a constant value, the model may be preprocessed to simplify it. This preprocessing step reduces the matrix dimensions for each variable with a constant value assigned. Equation (2.12) shows the analytical expressions for a function with 3 variables, where a constant value is assigned to the variable y, resulting in a function with 2 variables. The 3-dimensional matrix P has been converted to a 2-dimensional matrix Q.

$$f(x,y,z) = \sum_{i} \sum_{j} \sum_{k} P_{ijk} \cdot x^{i} y^{j} z^{k} \rightarrow y = k \rightarrow f(x,z) = \sum_{i} \sum_{k} Q_{ik} \cdot x^{i} z^{k}$$

$$\rightarrow Q_{ik} = \sum_{j} P_{ijk} \cdot k^{j}$$

(2.12)

Another computational advantage is that the model can be easily differentiated respect to any of its variables, to obtain the rate of change of the function. (2.13) shows an example of polynomial of two variables (x, y), with an m by n parameter matrix (P). The function is differentiated respect to variable y, getting a new polynomial function, where the parameter matrix (Q) was reduced to m by n-1, and each new parameter  $(Q_{ij})$  can be easily computed from the original ones  $(P_{ij})$ .

$$f(x,y) = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} P_{ij} \cdot x^{i} y^{i} \rightarrow \frac{\partial f(x,y)}{\partial y} = \sum_{i=0}^{m-1} \sum_{j=1}^{n-1} P_{ij} \cdot x^{i} \cdot j \cdot y^{j-1} = \sum_{i=0}^{m-1} \sum_{j=0}^{n-2} Q_{ij} \cdot x^{i} \cdot y^{j}$$

$$\Rightarrow Q_{ij} = (i+1) \cdot P_{i(j+1)} \quad \forall 0 \le i < m, 0 \le j < n-1$$

(2.13)

## 2.3. Effective capacitance

The capacitance of each circuit node is key when analyzing its dynamic behavior as it determines the signal time evolution. Specifically, the capacitance has a direct relation to the voltage variation in time and the amount of charge required to change the voltage level of a node. In this way, the efficacy of a circuit behavior prediction is strongly conditioned to the accurate estimation of the nodes capacitance. Some of the most relevant digital circuit analysis that require accurate capacitance estimation are:

- Timing analysis

- Power consumption

- Crosstalk analysis

- SET propagation

When working with digital circuits synthesized using a standard cell library the most interesting capacitance value is that of the input nodes of each cell, because these kinds of circuits are typically analyzed at the cell-level. Even in some cases, the designer has no access to the internal implementation of the cell, becoming impossible to perform an analysis at transistor or physical-level.

The main issue with the input capacitance of a CMOS cell is that it is a dynamic value depending on the voltage at each node. Therefore the value of the input capacitance varies during a transition, and even depend on the voltage transition speed. Accounting for this dependence -such as is done by SPICE-like simulation- implies adopting highly complex models resulting in an extremely time consuming simulation. Therefore, it is desirable to compute a capacitance steady that models as accurate as possible the dynamic behavior of the real capacitor. From now on we will refer as *effective capacitance* to the equivalent steady value of the dynamic capacitance of a cell input. The components that contribute to the input capacitance of a CMOS logic gate are detailed next.

## 2.3.1. Capacitance components

The input capacitance of a standard cell has two main contributions when describing an isolated cell, i.e., without considering any capacitive effect of the surrounding cells and wires of the circuit. The first contribution, at the transistor-level, is due to the MOSFET parasitic capacitors of the transistors forming the cell. A second contribution at the cell-level comes from the capacitors

## Chapter 2: Timing analysis and SET propagation

formed by the layout layers (metals, poly-silicon and diffusion areas) and the insulating oxide between them. Besides these two contributions, in a real circuit, there are more capacitances to consider for a precise analysis, but these depend on the specific circuit topology and must be extracted at the circuit-level, falling outside the standard cell-modeling domain. In any case, the gates capacitances provide the more relevant contribution, except for the interconnect dominated sections such as clock trees and buses.

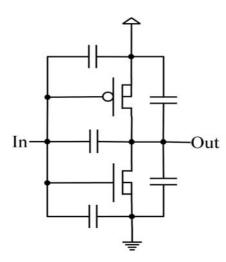

## 2.3.1.1. Transistor-level components

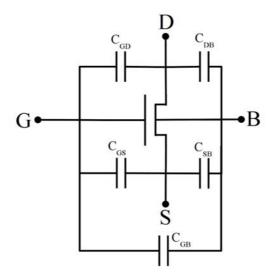

Regarding to the transistor-level contribution, basically a typical MOSFET transistor has five parasitic capacitors, as depicted in Fig. 2.5. They can be divided into two groups depending on if they are formed by an oxide between two conductors, or by a reverse polarized junction.

- Oxide capacitances: C<sub>gd</sub>, C<sub>gs</sub>, C<sub>gb</sub>.

- Junction capacitances: C<sub>db</sub>, C<sub>sb</sub>.

Figure 2.5: MOSFET parasitic capacitances

The oxide capacitances value depend on the transistor operation region, except for the component due to the gate and both diffusion regions (source and drain) overlap. This capacitance component is constant independently of the operation region, depends only on the overlapped area and the oxide coefficient, as shown in (2.14).

$$C_{overlap} = C_{ox} \cdot W \cdot L_D \tag{2.14}$$

where  $C_{ox}$  is the capacitance coefficient of the oxide, W is the transistor width, and  $L_D$  is the overlapping length between the gate and the diffusion.

The components depending on the operation region are due to the capacitor created between the gate and the channel being reason for its dependence on the operation region due to the channel shape variation. Table 3.1 summarizes the value of each oxide capacitance depending on the operation region specifying both the overlapping and channel components.

**Cut-off** Capacitance Linear **Saturation**  $C_{ox}WL$ 0  $C_{GB}$ 0  $0 + C_{ox}WL_{D}$  $0.5C_{ox}WL + C_{ox}WL_{D}$  $C_{ox}WL_{D}$  $C_{GD}$  $C_{GS}$  $0 + C_{ox}WL_{D}$  $0.5C_{ox}WL + C_{ox}WL_{D}$  $(2/3)C_{ox}WL + C_{ox}WL_{D}$

Table 2.1: Capacitance components

The junction capacitances value is even more complex than the oxide capacitances. In addition to the junction area, their value depends on the doping coefficient of the semiconductor and the voltage of each junction side. However, since these capacitances are created between the substrate and the diffusion areas (drain and source), their contribution to the input capacitance of a cell is small, since the input of a CMOS cell is always connected to the gate of the transistors.

During a rising or falling transition, the transistors that form a CMOS gate pass through the three regions of operation. Some transistors transition from cut-off to saturation, and others do in the opposite direction. The oxide capacitances change their value during the transition, together with the junction capacitances that have a voltage dependent value, giving the dynamic equivalent capacitance of the CMOS cell. Fig. 2.6 shows a schematic of a CMOS inverter, including the parasitic capacitors affecting its operation. Some of the transistors parasitic capacitors have no impact because they have both terminals shorted, like the nMOS bulk-source capacitance.

## Chapter 2: Timing analysis and SET propagation

Figure 2.6: Inverter capacitances

As already stated, the electrical-level simulators, use extremely complex transistor models that include the capacitive parasitic effects. However, this level of accuracy is paid with a huge computation time, due to the complexity of the model equations. These kinds of simulations are unaffordable for large circuits, and require to be simplified at the expense of a lower accuracy in the estimation.

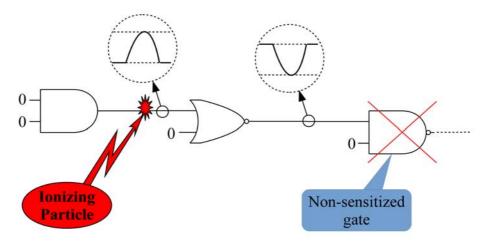

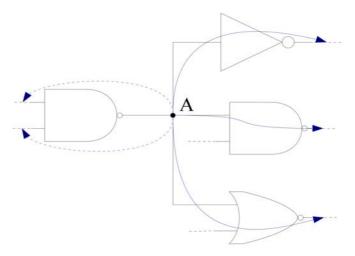

## 2.4. SET Propagation

A soft-error in a digital circuit is a circuit behavior alteration that occurs only during the circuit operation, usually caused by a dynamic event that impact circuit operation. Soft-errors are not associated to any physical defect in the circuit structure due to manufacturing errors or to inherent aging effects. Furthermore, soft-errors are usually not reproducible due to its dynamic nature and, since there is no physical defect in the circuit structure, they cannot be detected through a periodic circuit test, and its time occurrence cannot be predicted.

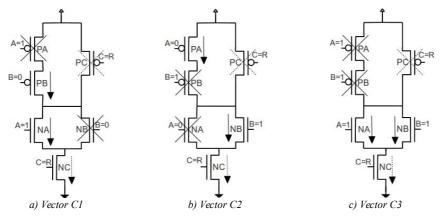

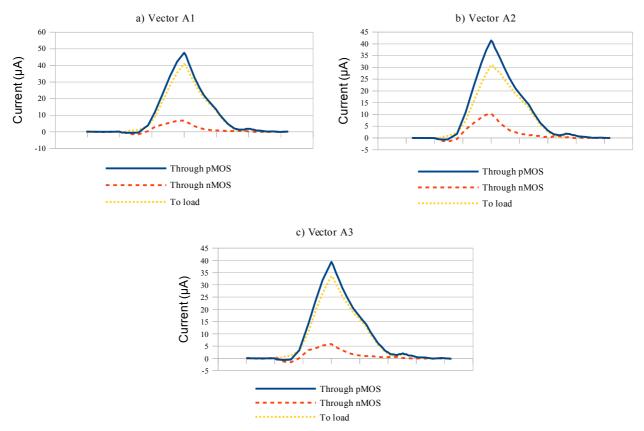

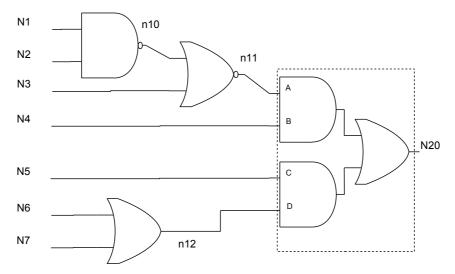

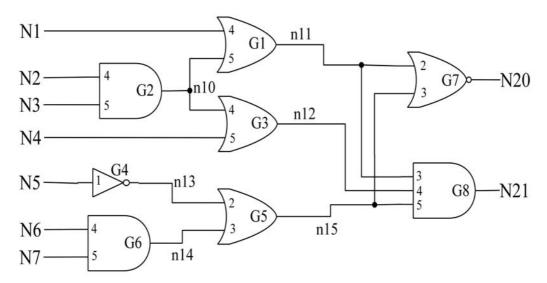

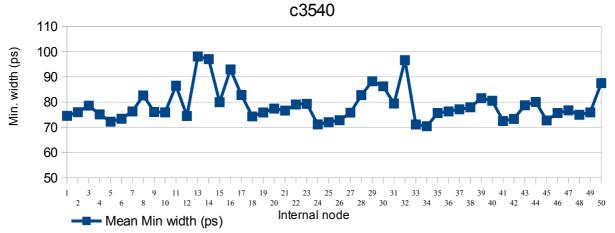

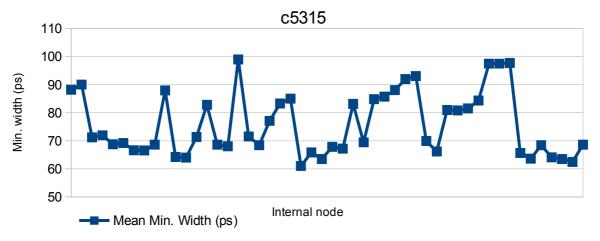

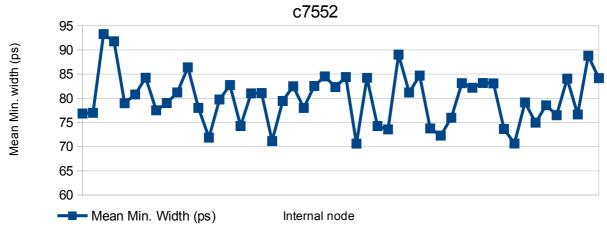

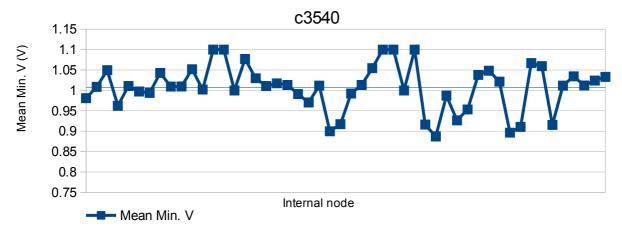

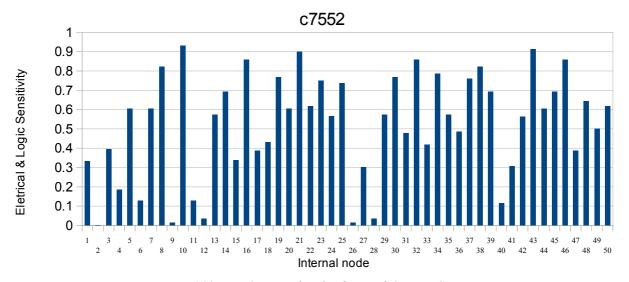

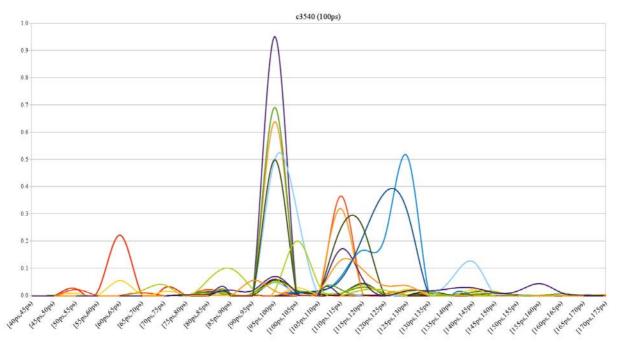

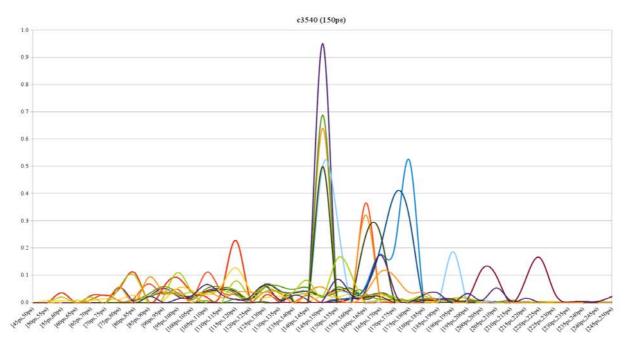

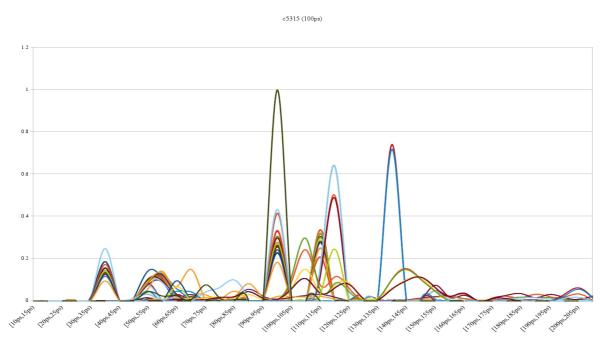

A source of soft-errors whose importance is growing due to technology scaling is alpha-particle and neutron strikes. Main sources are either contaminants from the circuit encapsulation, or cosmic radiation, i.e., high-energy particles coming from the space. Circuits operating outside the atmosphere protection, like space probes and artificial satellites, are specially affected by soft-errors. However, IC miniaturization is making soft-errors a concern even for sea-level applications.